고정 헤더 영역

상세 컨텐츠

본문

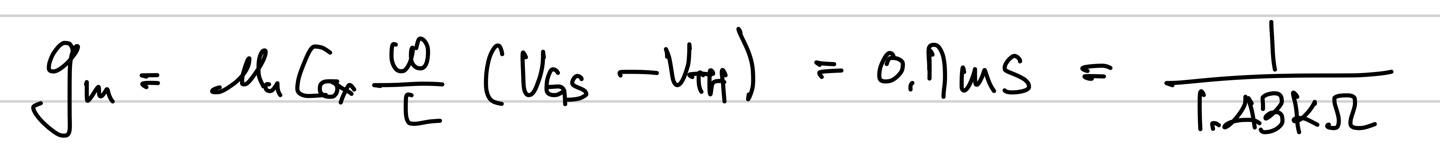

-Large Singal & Small Signal Modles (In Saturation region)

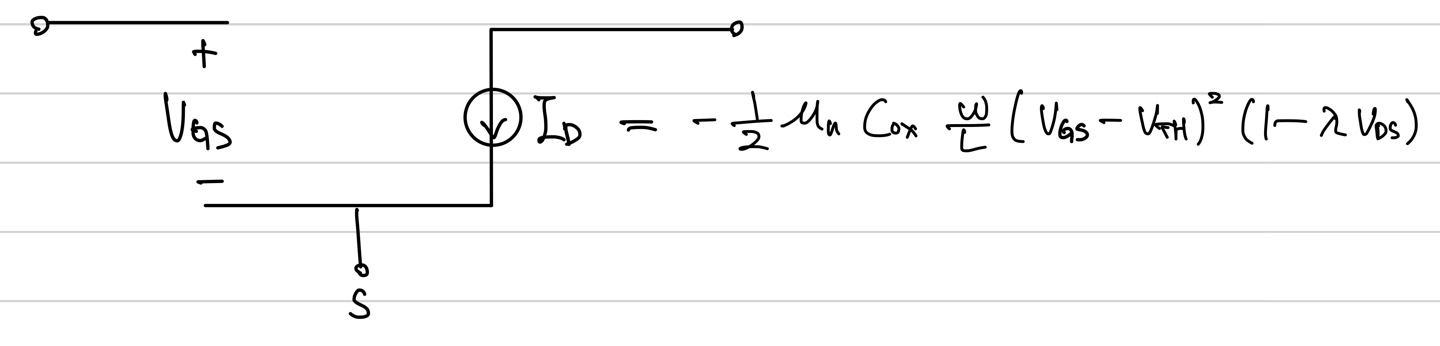

Large Signal model의 경우 아래와 같다.

이때 전류의 값은 Id의 값으로 channel length modulation 또한 포함한다.

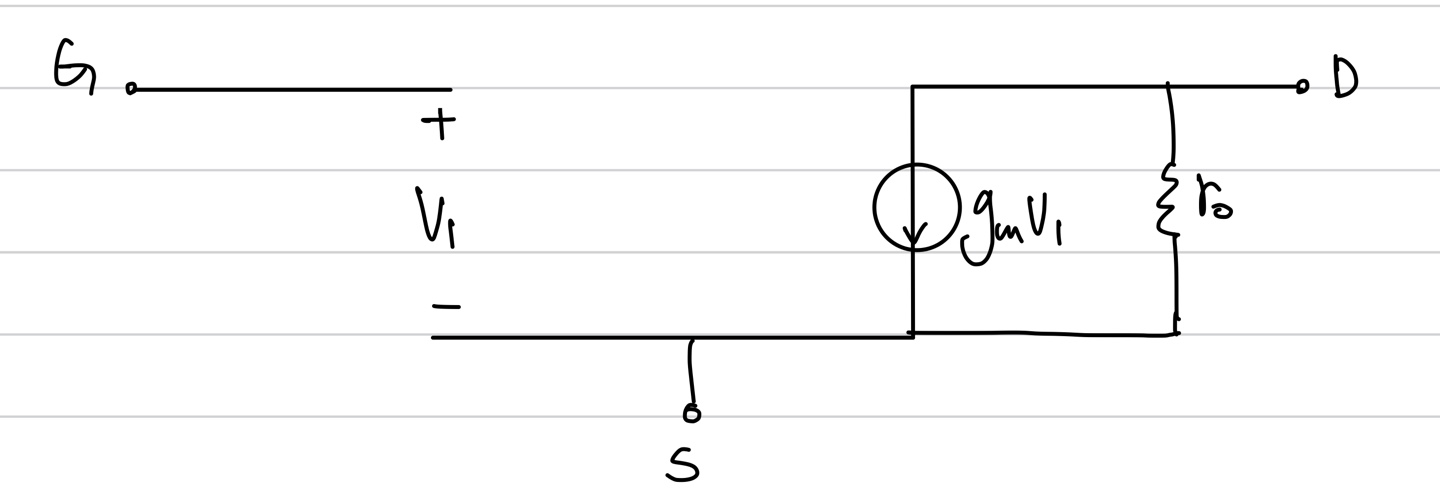

Small Signal model의 경우 아래와 같다.

이는 V1이라는 Vgs의 변화에 따라 gm을 곱해서 얻어지는 전류를 나타낸 것이다.

small signal model을 만들때 constant voltage source는 short로 constant current source는 open으로 바꿔 주면 된다. 이는 BJT bipolar transistor에서와 같다.

EX)

위의 회로를 small signal model로 나타내 보자. 그럼 우선 constant voltage source를 short으로 바꾸어 주고 나서 소신호 모델로 바꾸어 주면 아래와 같다.

-General Procedure for constructing a small-signal model

1) Apply proper bias voltages to the device

우선 적절한 biasing을 해준다.

2) Increment the voltage difference between two terminals

두 터미널 사이의 전압의 값을 증가시킨다. 위의 그림에서는 Vgs의 값을 증가시켰다.

3) Measure all current increment

전류의 변화량을 측정한다.

4) Model this change by a proper electrical device

이 변화를 적절한 device로 바꾸어 준다. (저항, 다이오드 등등)

그래서 위의 그림에서 전압의 변화에 따라 gmV만큼의 전류가 변화함으로 dependant current source로 생각하여 아래와 같은 small signal model을 만들 수 있다.

이를 바탕으로 channel length modulation을 포함한 small signal model을 찾아보자. 우선 2번에서 처럼 전압을 상승시키는데 channel length modulation은 Vds의 전압에 의해 pinch off 가 생기면서 발생하는 현상임으로 Vds의 전압을 상승시키면 전류의 값이 미세하게 증가하게 될 것이다.

이를 수식으로 나타내면 아래와 같다.

위의 식을 통해 전류랑을 측정하였으므로 이 변화에 대해 구해보면

이와 같고 이를 정리하면 변화가 저항의 형태로 나타남을 확인할 수 있다. 그래서 ro라는 임의의 저항으로 나타내고 이 값은 channel length modulation을 small signal model에서 표현하는 값이다. 그리고 이 전압과 전류는 drain과 source 사이에 발생한 변화임으로 아래와 같이 small signal modle을 그려준다.

gm을 구할때 channel length modulation을 포함하지 않고 구했는데 gm을 생각할 때는 굳이 고려하지 않고 넘어가자.

EX)

위의 조건에서 small signal model을 구해보자.

우선 여기서 V1의 값은 Vgs로 1.2V이다. 이를 이용해 gm의 값을 구하면 아래와 같다.

ro를 구하기 위해 Id의 값을 구하기 위해 아래의 식을 이용하여 정리하면

-MOS Device Type

지금까지 우리는 아래와같은 상태에서

MOSFET을 분석하였다. 이를 NMOS라 부르고 bipolar transistor에서 처럼 PMOS또한 존재한다.

PMOS는 NMOS와 반대로 substrate가 n type이고 source와 drain 또한 hole로 doping이 되어 있다. 이때 gate의 전압은 음의 값을 갖는다. 그로 인해 전자가 밀리면서 depletion region이 만들어지게 된다. 그 후에 Vth를 넘게 되면 hole로 이루어진 channel이 만들어진다. 이 channel에 전류가 흐르려면 hole이 source에서 drain으로 이동해야 하므로 Vds<0값을 갖게 된다.

PMOS는 왼쪽과 같이 표현하는데 보통 전압이 높은 쪽을 위로 표현함으로 오른쪽과 같이 표현한다. 또한 여기서 특징은 전류의 방향을 drain에서 source로 그리는데 원래는 PMOS 화살표 방향으로 전류가 흐르기 때문에 전류는 음의 값을 갖는다.

Saturation region인 경우 전류의 값은 아래와 같다.

여기서 Vds는 음의 값이므로 위와 같이 표현하고 Vgs도 원래는 반대로 해줘야되지만 어차피 제곱임으로 그대로 쓴다.

이제 PMOS의 large signal model을 구해보면 아래와 같다.

PMOS의 상태를 시각화해서 표현하면 아래와 같다.

saturation region이 되는 조건은 NMOS와 같다. 그저 부호 때문에 익숙하지 않기는 한데 연습하면 괜찮을 듯하다.

-Small Signal Model of PMOS

PMOS와 NMOS의 small signal model은 정확히 일치한다.

EX)

위의 회로를 small signal model로 나타내 보자. 그럼 아래와 같은 결과를 얻을 수 있다.

이때 이 회로에서 단순히 계산해서 풀면 문제에 따라 풀리긴 하겠지만 쉽지 않을 수도 있다. 그래서 꼭 차근차근 회로의 관계를 생각해 볼 수 있어야 한다. V1과 V2를 살펴보면 2개의 node를 서로 공유하고 있다. 심지어 +극에서 하나 -극에서 하나 이렇게 완벽히 일치하는 모습을 보이고 있다. 그러므로 V1=V2라고 생각할 수 있다. 또한 gmV도 각각의 node를 공유하고 있으므로 이는 병렬로 연결되어 있다고 생각할 수 있다. V1과 V2도 마찬가지로 병렬로 연결되어 있다고 생각할 수 있다. 물론 전압이 병렬로 연결되면 같아야 한다. ro1과 ro2도 gmV와 마찬가지로 노드를 공유함으로 이 또한 병렬로 연결되어 있다. 이러한 조건들을 바탕으로 해석을 해야 문제를 더 쉽게 풀 수 있으므로 꼭 한 번씩 관계를 생각해보고 문제에 접근하길 바란다.

V/R

윤.

'윤. 전기전자 > MOS Transistor' 카테고리의 다른 글

| Lecture 35. Common Source Stage 1 for MOSFET (1) | 2021.02.03 |

|---|---|

| EX 6-16 , Problem 39 (0) | 2021.02.02 |

| Lecture 33. Large-Signal & Small-Signal Model for MOSFET (0) | 2021.02.01 |

| Lecture 32. Biasing, Transconductance (0) | 2021.01.31 |

| Lecture 31. MOS Characteristics 2 (0) | 2021.01.31 |

댓글 영역