고정 헤더 영역

상세 컨텐츠

본문 제목

Lecture 23. Examples of High-Speed Circuits, Response of Common Base/Gate stage

본문

-Frequency Response of CB/CG stages

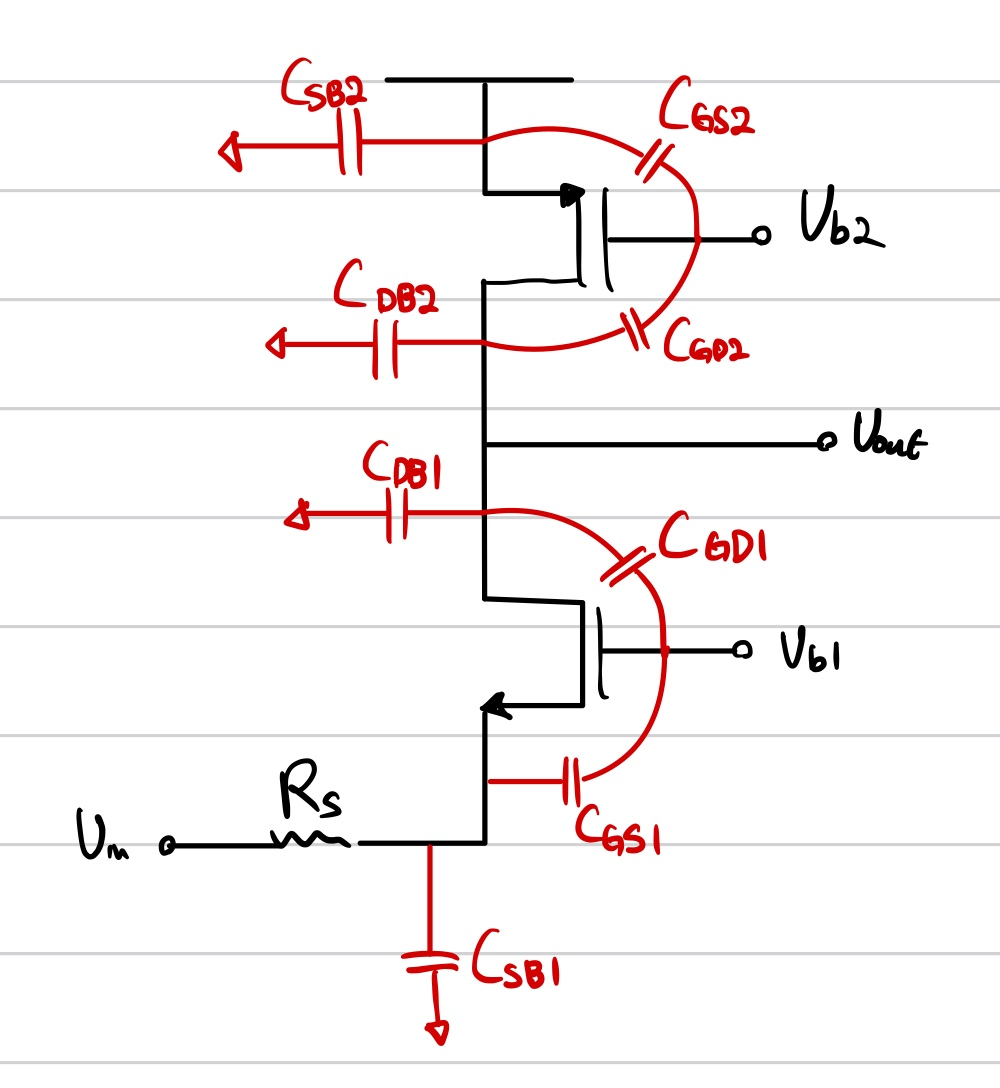

위의 회로는 CE/CG stage이다. 여기서 parasitic cap을 그려놨는데 없앨 수 있는 것을 없애고 합치면 아래와 같다. 그리고 Re와 Rs는 이전 stage의 저항을 의미한다.

여기서 pole inspection을 이용하면 input에서 Cap은 Cpi이고 저항의 값은 아래와 같다.

그 결과 Wp,in은 아래와 같다.

output의 경우 Ccs+Cu가 cap의 값이고 R은 Rc이다. 그 결과 아래와 같다.

여기서 계속 early effect 혹은 channel length modulation이 없을 때를 가정하여 값을 구하고 있는데 이는 나도 솔직히 잘은 모르겠지만 해당 조건이 없으면 더 복잡한 값으로 계산이 되어야 한다고 한다. 그래서 우리는 pole을 추정할 때 사용하는 것임으로 대략적으로만 이용하지 이를 너무 신뢰하지는 말자.

EX)

위의 회로에서 우선 Vb1과 Vb2를 GND로 만들어주면 없애던지 합칠 수 있다.

이를 바탕으로 Vin에서 Wp,in을 구하면 아래와 같다.

이제 Wp,out을 구하려고 하는데 두 가지 경우를 생각해봐야 한다. channel length modulation의 여부에 따라 값이 다르게 나온다. ro를 추가하면 아래와 같다.

여기서 만약 channel length modulation이 없는 경우를 생각해보자. 그렇게 되면 ro는 무한대로 없어지고 R의 값이 무한대로 나타나게 된다. 이는 Wp,out=0임을 말해준다.

channel length modulation이 있는 경우

이를 고려하여 아래와 같은 결과를 얻을 수 있다.

하지만 좀 말이 이상한데 실제로 계산을 하게 되면 위의 결과가 아니라고 한다.

Channel Length Modulation을 고려하게 되면 식이 훨씬 복잡해진다. 여기서 중요한 것은 대략적으로 pole의 상대적인 위치를 파악하는 것이 중요하다. 그래서 나중에 설계를 할 때 input 혹은 output이 dominant pole인지 파악하기 위해서 사용하는 것이 더 중요한 것 같다.

V/R

윤.

댓글 영역